全定制集成电路设计流程详解

集成电路(IC)是现代电子设备的核心,其设计方法主要分为全定制、半定制和基于标准单元的设计。其中,全定制集成电路设计以其对性能、功耗和面积的极致优化,在高端处理器、模拟/射频电路和存储器等关键领域占据不可替代的地位。本课件将系统阐述全定制集成电路设计的完整流程。

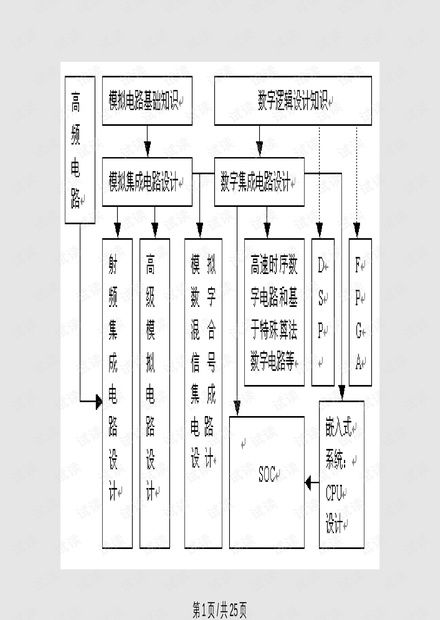

一、设计流程概述

全定制设计是一种从晶体管级开始,对电路中的每一个器件(晶体管、电阻、电容等)及其互连进行手工精心设计和优化的方法。其核心目标是实现最佳的电路性能(如速度、功耗、增益等)和最小的芯片面积。整个流程环环相扣,通常遵循“自顶向下设计,自底向上验证”的原则。

二、主要设计阶段

1. 系统规划与指标定义

* 输入:市场/产品需求、系统架构。

- 活动:明确芯片的功能、性能指标(如工作频率、功耗预算)、接口协议、工艺节点选择等。

- 输出:设计规格说明书(Specification)。

2. 电路设计与仿真

* 输入:设计规格。

- 活动:

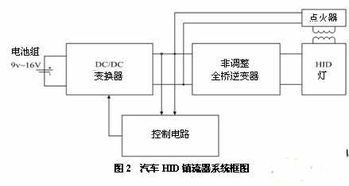

- 架构设计:确定整体电路架构,如流水线级数、存储器结构等。

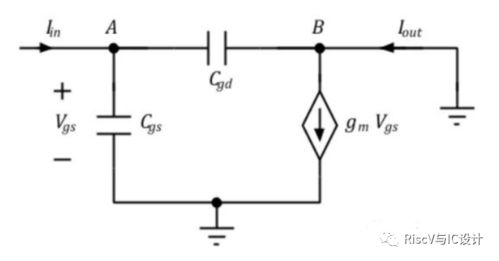

- 晶体管级电路设计:使用电路图编辑器(Schematic Editor)绘制每一个功能模块(如反相器、运算放大器、锁存器)的详细电路图。设计师需要根据工艺库模型,手动确定每个晶体管的宽长比(W/L)。

- 电路仿真:利用SPICE或类似的仿真工具,对设计好的电路进行严格的仿真分析,包括直流分析、瞬态分析、交流分析、噪声分析等,以验证其功能、时序、功耗和可靠性是否满足指标。此阶段需要进行大量迭代优化。

- 输出:经过验证的电路原理图(Schematic)和仿真报告。

3. 版图设计

* 输入:已验证的电路原理图、工艺设计规则(Design Rule)。

- 活动:

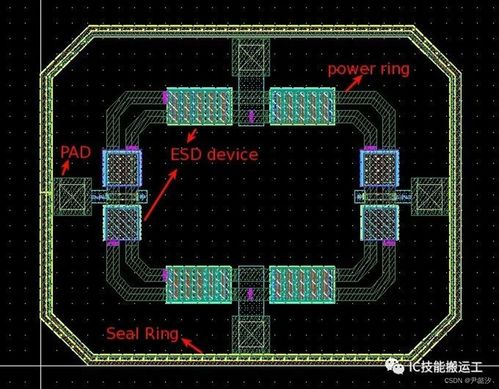

- 物理实现:使用版图编辑器(Layout Editor),根据电路图,在遵守代工厂提供的物理设计规则(最小线宽、间距、覆盖等)的前提下,手工绘制构成每个晶体管的几何图形(多晶硅、有源区、金属连线、接触孔等),完成所有器件的物理布局和互连。

- 关注要点:匹配性(如差分对)、寄生效应(电阻、电容)、信号完整性、电源网络规划、面积优化。

- 输出:芯片的物理版图(GDSII格式文件)。

4. 物理验证与后仿真

* 输入:物理版图、电路原理图、工艺文件(设计规则文件DRC、电路提取文件LVS、寄生参数提取文件PEX)。

- 活动:

- 设计规则检查(DRC):验证版图是否符合制造工艺的几何规则,确保可制造性。

- 版图与原理图一致性检查(LVS):验证绘制出的物理版图是否与原始电路原理图在电气连接上完全一致。

- 寄生参数提取(PEX):从最终版图中提取出连线的寄生电阻和电容。

- 后仿真(Post-layout Simulation):将提取出的寄生参数反标回电路网表,再次进行电路仿真。这是最接近芯片实际性能的仿真,用于确认版图引入的寄生效应没有导致电路性能超标。

- 输出:干净的版图(通过所有检查)和最终的性能验证报告。

5. 数据交付与流片

* 输入:通过所有验证的最终版图数据(GDSII)。

- 活动:将GDSII数据交付给集成电路制造厂(Foundry)。

- 输出:交付数据包,进入芯片制造阶段(光刻、刻蚀、离子注入、封装测试等)。

三、全定制设计的挑战与优势

- 挑战:

- 设计周期长:手工设计、迭代和验证工作极其耗时。

- 设计成本高:需要资深设计工程师,且流片费用昂贵。

- 复杂性管理难:对于大规模电路,手工设计和管理复杂度极具挑战。

- 优势:

- 性能最优:可以实现最高的运行速度、最低的功耗和最小的面积。

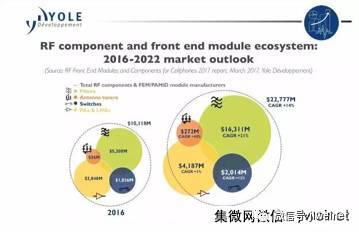

- 灵活性最高:不受预定义单元库的限制,可以设计任何特殊结构的器件和电路。

- 适用于模拟/混合信号电路:模拟电路对器件特性和匹配性要求极高,必须采用全定制方法进行精细控制。

四、

全定制集成电路设计是一个高度专业化、迭代密集的创造性过程。它要求设计者兼具深厚的电路理论知识和丰富的工程实践经验。尽管面临周期和成本的挑战,但在追求极致性能、能效以及设计模拟、射频、存储器和高端数字核(如CPU/GPU中的关键路径)时,全定制设计仍然是无可替代的核心技术。随着工艺节点的不断演进,其设计方法和EDA工具也在持续发展,以应对日益增长的复杂性和物理效应挑战。