静电放电(ESD)是集成电路(IC)设计中不可忽视的关键可靠性问题。在芯片的制造、封装、测试及日常使用中,静电电荷的积累和瞬间释放可能对微小的晶体管和互连线造成不可逆的损伤,导致芯片功能失效。因此,专业的ESD保护电路设计是确保芯片鲁棒性和产品良率的基石。

一、ESD威胁与保护原理

ESD事件产生的瞬间高压(可达数千伏)和大电流,会通过芯片的引脚(I/O、电源、地)注入。其破坏机制主要包括热损伤(电流焦耳热导致金属熔断或多晶硅烧毁)和电过应力(栅氧击穿)。ESD保护电路的核心思想,是在敏感的内部核心电路与外部引脚之间,构建一条可控的低阻抗放电路径。当ESD事件发生时,保护器件能迅速开启(通常在纳秒级),将大部分ESD电流旁路到地或电源轨,从而将内部电路节点上的电压钳位在安全水平以下。

二、经典ESD保护电路结构与器件

- 基于二极管的结构:这是最常用的初级保护方式。在I/O引脚与VDD之间放置正向二极管,在I/O引脚与VSS之间放置反向二极管(或利用寄生BJT)。ESD正脉冲时,I/O-to-VSS二极管导通;负脉冲时,VDD-to-I/O的寄生路径或I/O-to-VDD二极管导通。其优点是面积小、速度快,但钳位能力有限。

- 栅极接地NMOS(GGNMOS):这是业界标准的片上ESD保护器件。在ESD应力下,其寄生NPN双极晶体管会开启(雪崩击穿触发),进入snap-back特性区域,从而在较低维持电压下泄放大电流。其设计需精心优化漏极接触孔到栅的距离、宽度等参数以调整触发电压和鲁棒性。

- 可控硅整流器(SCR):具有极高的单位面积电流泄放能力(是GGNMOS的5-10倍),非常适合用于面积受限的高压或高频引脚保护。但其触发电压通常较高,且存在闩锁风险,需要与其它电路配合使用。

- 电源钳位(Power Clamp)电路:用于保护VDD与VSS之间的电源域。它不是始终导通,而是通过RC定时器等检测电路感知ESD快速的电压上升沿(相对于正常上电),然后触发一个大尺寸的MOSFET(如Big FET)瞬间导通,为电源轨之间的ESD电流提供主泄放通道。

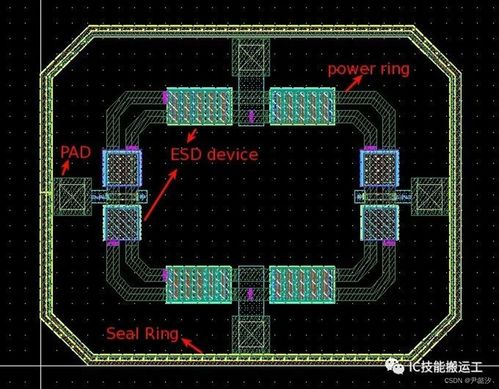

三、全芯片ESD保护网络设计

一个完整的芯片ESD防护是一个系统级网络:

- 初级保护:位于焊盘附近,第一时间响应,承受主要电流冲击。

- 次级保护:位于初级保护与内部电路之间,提供二次钳位,并防止初级保护开启时产生的过冲电压。

- 电源钳位:均匀分布在电源网络上。

- 互连设计:所有保护路径必须使用足够宽和低阻的金属线连接,避免互连电熔断成为薄弱环节。

- 核心电路的自保护:对于非常敏感的输入栅(如射频输入),有时需在内部增加小尺寸的分布式二极管或电阻进行细粒度保护。

设计时必须确保在任何两个引脚组合(如I/O-I/O, I/O-VDD, VDD-VSS等)之间,都存在一条完整的、鲁棒的低阻抗ESD电流路径,这被称为“ESD设计窗口”的满足。

四、挑战与协同设计考虑

随着工艺节点不断演进至纳米级和 FinFET 时代,ESD设计面临新挑战:薄栅氧更易击穿、器件耐压降低、设计窗口变窄、寄生效应更复杂。ESD设计必须与工艺特性、封装形式、系统应用场景协同考虑。版图设计中的门锁(Latch-up)预防、天线效应避免等也与ESD息息相关。

ESD电路设计是集成电路可靠性工程的核心。它要求设计者深入理解半导体器件物理、工艺制程、电路架构和测试标准(如HBM, CDM, MM),通过精心设计保护网络、优化器件版图,在保护性能、速度、面积和寄生效应之间取得最佳平衡,从而铸造出坚固耐用的芯片。对于更多实践细节、仿真方法和最新研究进展,开发者们常在CSDN等技术社区博客中分享和交流经验,共同推动这一关键领域的技术进步。