半导体制造和集成电路设计是现代信息技术的基石,两者相互依存、共同演进,塑造了今日的数字世界。其发展历程,是一部浓缩的科技创新史诗。

一、 半导体制造的黎明与工艺奠基(1940s-1960s)

半导体制造的历史始于1947年贝尔实验室的威廉·肖克利、约翰·巴丁和沃尔特·布拉顿发明点接触晶体管,替代了笨重、低效的真空管。肖克利于1951年发明了更稳定、易制造的双极结型晶体管(BJT),为半导体工业奠定了基础。

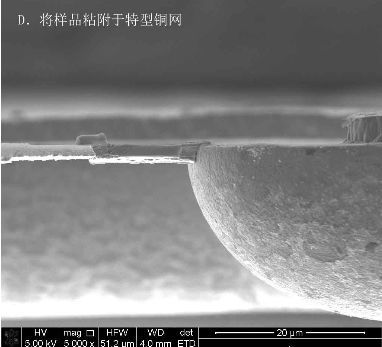

真正的革命发生在1958-1959年,德州仪器的杰克·基尔比和仙童半导体的罗伯特·诺伊斯分别独立发明了集成电路(IC)。诺伊斯提出的基于硅的平面工艺(光刻、氧化、扩散)尤为重要,它使得在单一硅片上批量制造多个晶体管和互连线成为可能,开启了微电子时代。早期的制造工艺以PMOS和NMOS技术为主,线宽在几十微米级别。

二、 设计方法的萌芽与摩尔定律的提出(1960s-1970s)

随着集成电路上晶体管数量的增加,设计复杂性开始显现。最初的电路设计是手工完成的,工程师在图纸上绘制每个晶体管和连线,这被称为全定制设计。

1965年,仙童半导体的戈登·摩尔提出了著名的摩尔定律,预言集成电路上可容纳的晶体管数量约每18-24个月翻一番。这一定律不仅成为半导体制造工艺发展的蓝图,也对设计方法提出了持续升级的要求。

这一时期,标准单元库和门阵列等半定制设计方法开始出现,设计者可以复用预先设计好的逻辑门单元,提高了设计效率。

三、 VLSI时代与EDA工具的兴起(1970s-1980s)

制造工艺进入超大规模集成电路(VLSI) 时代(晶体管数量达到数万至数十万)。CMOS技术因其低功耗、高集成度优势,逐渐取代NMOS成为主流。光刻技术不断进步,线宽进入微米级。

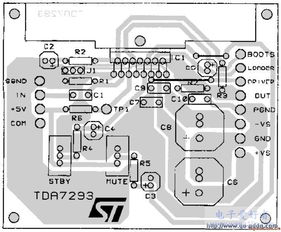

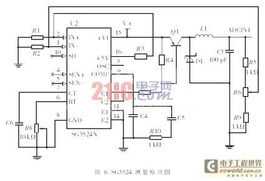

手工设计已无法应对VLSI的复杂度。这催生了电子设计自动化(EDA) 产业的诞生。公司如Calma、Daisy、Mentor Graphics(现Siemens EDA)等开发了计算机辅助设计(CAD)工具,用于电路图输入、逻辑模拟和版图设计。

设计方法学也迎来突破。卡弗·米德和林恩·康威在1980年出版的《超大规模集成电路系统导论》中,提出了将设计流程抽象化、规范化的理念,强调了设计规则与制造工艺分离的重要性,极大地推动了设计生产力的解放。

四、 ASIC、SoC与深亚微米制造(1990s-2000s)

制造工艺迈向深亚微米(小于0.5微米)。专用集成电路(ASIC) 设计盛行,企业可根据特定需求进行定制。更重要的趋势是系统级芯片(SoC) 概念的成熟,即把整个系统(处理器、内存、接口、专用功能模块等)集成到单一芯片上。

这要求设计方法发生根本变革:硬件描述语言(HDL),如VHDL和Verilog,成为主流设计入口。设计流程从寄存器传输级(RTL) 描述开始,通过逻辑综合、布局布线等EDA工具自动生成版图。IP核(知识产权核)复用成为SoC设计的关键,减少了重复开发。

制造端,铜互连(替代铝)、化学机械抛光(CMP)、浸没式光刻等关键技术相继突破,支撑着摩尔定律持续前行。

五、 纳米时代与协同优化新范式(2000s至今)

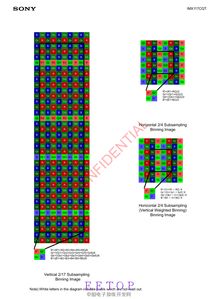

工艺节点进入纳米尺度(90nm、65nm直至当今的3nm、2nm)。物理效应(如短沟道效应、漏电流、互连线延迟、工艺波动)带来的挑战空前严峻,单纯的特征尺寸缩小带来的性能增益放缓。

这促使制造与设计深度融合,走向设计-工艺协同优化(DTCO) 和系统-工艺协同优化(STCO)。制造上,引入了高K金属栅极(HKMG)、FinFET(鳍式场效应晶体管)、GAA(环绕栅极) 等革命性晶体管结构,以及多重曝光、EUV(极紫外)光刻等尖端工艺。

设计方面则呈现多元化:

- 平台化与IP高度复用:基于Arm、RISC-V等处理器内核的SoC平台设计成为常态。

- 异构集成:通过先进封装技术(如2.5D/3D IC、Chiplet芯粒)将不同工艺、功能的芯片模块集成在一起,从“系统级芯片”走向“芯片级系统”。

- 软硬件协同与领域专用:针对AI、自动驾驶、HPC等特定领域,设计专用架构(如DSA、NPU),并需要算法、软件、硬件架构与工艺的紧密协同。

- EDA智能化:AI/ML技术被引入EDA工具,用于加速设计探索、优化功耗性能面积(PPA)和预测制造缺陷。

###

半导体制造与集成电路设计的历史,是一部从器件物理突破,到工艺制程精进,再到设计方法抽象化、自动化、系统化的演进史。面对物理极限和经济成本的挑战,未来的发展不再仅仅依赖于尺寸微缩,而更依赖于架构创新、材料突破、先进封装以及设计-制造-应用全链条的深度协同。这条演进之路,仍将继续引领着计算能力的飞跃和数字社会的变革。