集成电路(IC)设计,作为信息技术的基石,正处在一个激动人心的十字路口。随着摩尔定律逐渐逼近物理与经济的双重极限,单纯依靠工艺节点的微缩来提升性能、降低功耗的模式已面临巨大挑战。这迫使全球半导体产业必须从设计理念、架构、方法学和工具等多个维度进行根本性的创新。以“新思路”驱动集成电路设计,已成为行业持续发展的核心命题。

一、从同构到异构:架构创新的主旋律

传统上,提升芯片性能主要依赖于在单一硅片上集成更多、更快的同构计算核心(如CPU)。面对多样化的计算负载(如AI推理、图形渲染、信号处理),通用核心的效率瓶颈日益凸显。因此,异构集成成为最显著的新思路。

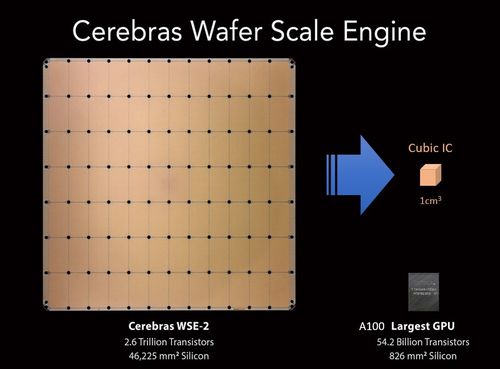

- 芯粒(Chiplet)与先进封装:这是打破“大芯片”制造良率瓶颈、实现灵活集成的革命性路径。设计思路从“设计一个巨型的单芯片”转变为“设计一个由多个特定功能芯粒(如计算芯粒、存储芯粒、I/O芯粒)通过先进封装(如硅中介层、3D堆叠)集成的系统”。这种方法允许混合使用不同工艺节点、不同材料的芯粒,实现最优的性能、功耗和成本组合,大大提升了设计灵活性和产品上市速度。

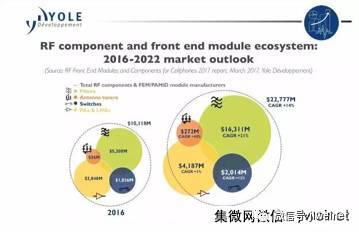

- 领域专用架构(DSA):针对特定应用领域(如人工智能、自动驾驶、5G通信)定制计算架构。例如,AI加速器(如TPU、NPU)通过设计专用的张量计算单元和内存 hierarchy,在处理AI工作负载时能效比远超通用CPU。未来的设计思路将更侧重于为垂直应用“量身定做”硬件。

二、从自动化到智能化:设计方法学的范式转移

电子设计自动化(EDA)工具是设计的“画笔”。新思路的核心是让这支画笔变得更加“智能”。

- AI驱动的设计自动化:机器学习(ML)技术正在渗透到设计的各个环节。从高层架构探索、逻辑综合、布局布线,到功耗和时序签核,AI算法可以学习海量历史设计数据与专家经验,快速预测设计结果、优化参数配置,甚至自动完成部分设计,将工程师从繁琐的试错中解放出来,极大缩短设计周期。例如,利用强化学习进行宏模块布局,其效果已可媲美甚至超越人类专家。

- 智能设计空间探索:面对复杂的系统级芯片(SoC)设计,设计空间巨大。新思路是利用智能算法(如贝叶斯优化、遗传算法)快速、自动地探索数以百万计的设计参数组合(如核心数量、缓存大小、电压频率),在性能、功耗、面积(PPA)等多目标约束下找到帕累托最优解。

三、从硬件定义到软件定义:软硬件协同的深度演进

“软件定义硬件”成为新的设计哲学。硬件不再是一个固定不变的实体,而是需要为上层软件和应用提供极致的灵活性和可编程性。

- 可重构计算:通过FPGA或粗粒度可重构阵列(CGRA),芯片的硬件功能可以在运行时根据软件需求进行动态配置。这种思路特别适合算法快速迭代、计算模式多变的场景,实现了高性能与高灵活性的统一。

- 开放的指令集与敏捷开发:RISC-V等开源指令集架构(ISA)的兴起,打破了传统架构的垄断,赋予了设计者更大的自由。结合敏捷硬件开发方法(如基于Chisel/Hardware Description Language的高级语言、更快的验证流程),使得从算法到定制化芯片的路径大大缩短,激发了芯片创新的长尾市场。

四、从性能至上到全面优化:设计目标的重新定义

除了追求极致的PPA,新的设计思路必须综合考虑更多维度的约束和目标。

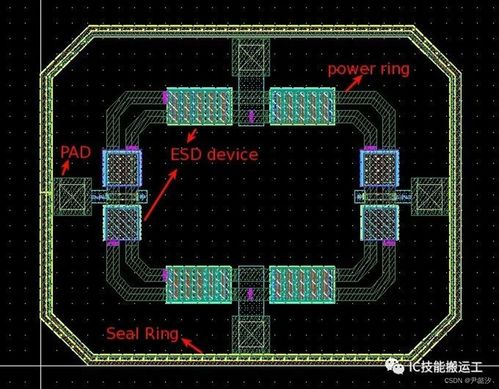

- 安全与可信设计:硬件安全成为“一等公民”。设计之初就必须融入安全考量,包括侧信道攻击防护、硬件信任根、物理不可克隆功能(PUF)、供应链安全等,实现“设计即安全”。

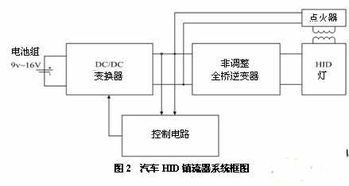

- 可靠性、可测性与可持续性:随着芯片应用于汽车、工业、航天等关键领域,高可靠性和可测试性设计至关重要。芯片全生命周期的能效和环境影响(绿色设计)也日益成为重要的设计指标。

###

集成电路设计的新思路,本质上是应对后摩尔时代挑战的系统性回应。它不再局限于晶体管层面的精雕细琢,而是上升到系统架构、跨学科融合和设计生态的层面。异构集成、智能化工具、软硬件协同以及多目标优化,共同构成了下一代集成电路设计的四大支柱。拥抱这些新思路,意味着从“如何画得更小”转向“如何画得更聪明、更高效、更贴合需求”,从而在日益复杂和多样化的全球半导体竞争中,开辟出新的航道,持续驱动数字世界的创新引擎。